服務(wù)熱線

0755-83044319

發(fā)布時間:2022-03-18作者來源:薩科微瀏覽:2835

一、3D 封裝將成為主要工藝

轉(zhuǎn)自:智東西

近日,中國臺灣工業(yè)技術(shù)研究院研究總監(jiān) Yang Rui 預(yù)測,臺積電將在芯片制造業(yè)再占主導(dǎo)地位五年,此后 3D 封裝將成為主要工藝挑戰(zhàn)。

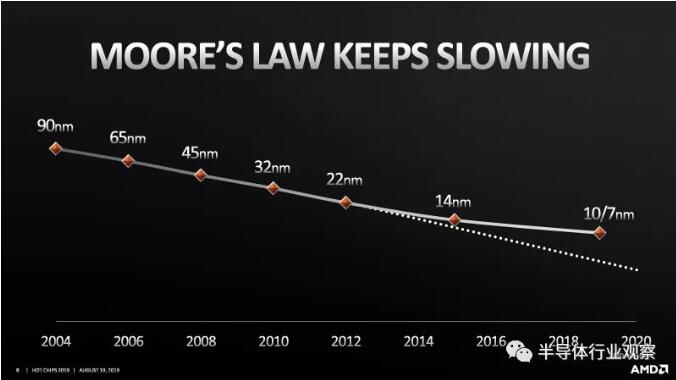

過去十年各種計算工作負載飛速發(fā)展,而摩爾定律卻屢屢被傳將走到盡頭。面對更家多樣化的計算應(yīng)用需求,為了將更多功能 " 塞 " 到同一顆芯片里,先進封裝技術(shù)成為持續(xù)優(yōu)化芯片性能和成本的關(guān)鍵創(chuàng)新路徑。

臺積電、英特爾、三星均在加速 3D 封裝技術(shù)的部署。今年 8 月,這三大芯片制造巨頭均亮出,使得這一戰(zhàn)場愈發(fā)硝煙四起。

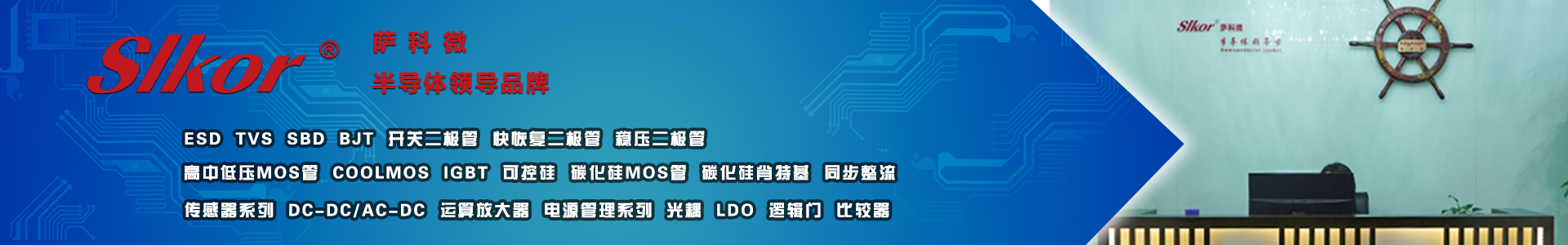

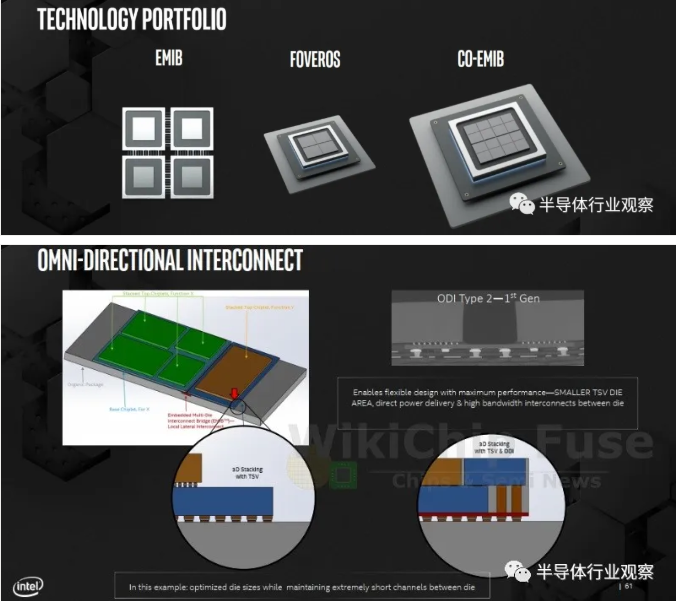

▲英特爾封裝技術(shù)路線圖

通過三大芯片制造巨頭的先進封裝布局,我們可以看到在接下來的一年,3D 封裝技術(shù)將是超越摩爾定律的重要殺手锏。

一、先進封裝:將更多功能塞進一顆芯片

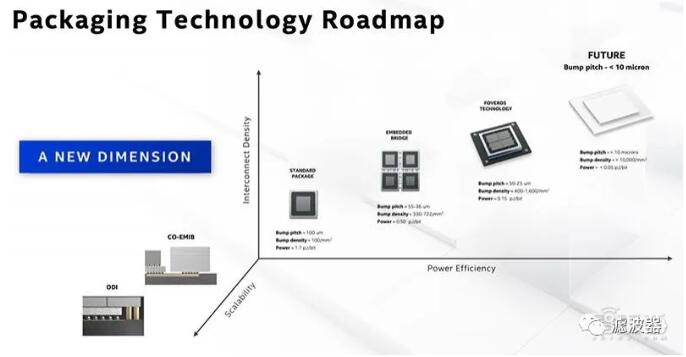

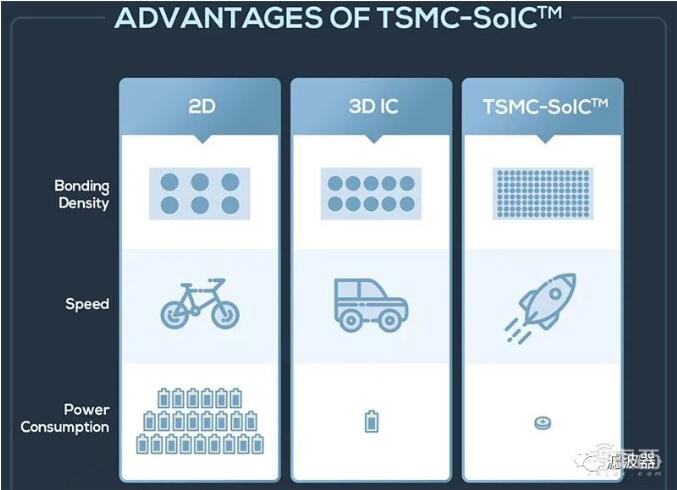

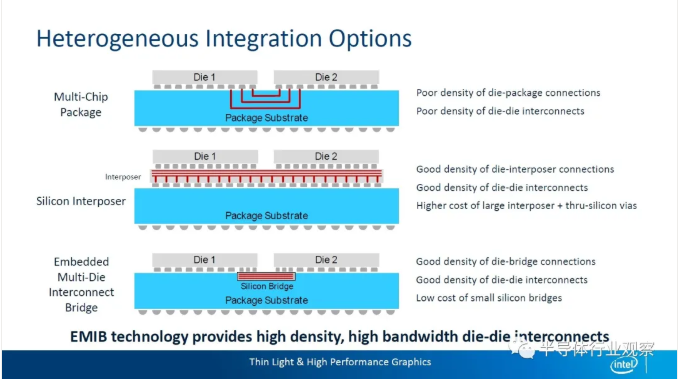

此前芯片多采用 2D 平面封裝技術(shù),但隨著異構(gòu)計算應(yīng)用需求的增加,能將不同尺寸、不同制程工藝、不同材料的芯片集成整合的 3D 封裝技術(shù),已成為兼顧更高性能和更高靈活性的必要選擇。

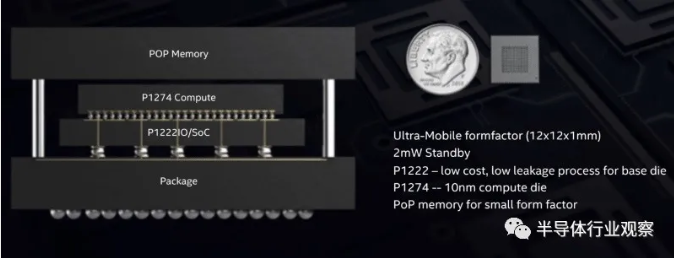

從[敏感詞] 3D 封裝技術(shù)落地進展來看,英特爾 Lakefield 采用 3D 封裝技術(shù) Foveros,臺積電的 3D 封裝技術(shù) SoIC 按原計劃將在 2021 年量產(chǎn),三星的 3D 封裝技術(shù)已應(yīng)用于 7nm EUV 芯片。

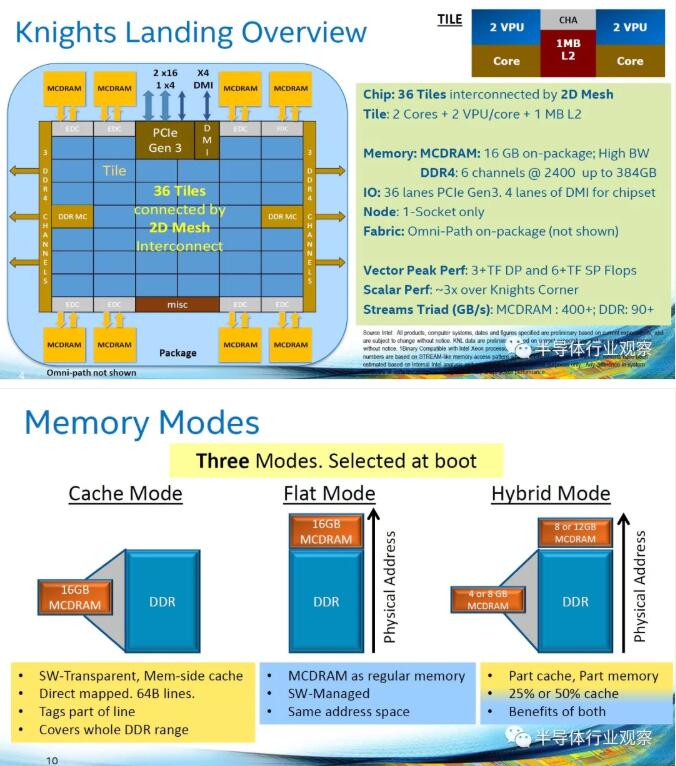

為什么要邁向先進封裝技術(shù)?主要原因有二點,一是迄今處理器的大多數(shù)性能限制來自內(nèi)存帶寬,二是生產(chǎn)率提高。

一方面,存儲帶寬的開發(fā)速度遠遠低于處理器邏輯電路的速度,因此存在 " 內(nèi)存墻 " 的問題。

在傳統(tǒng) PCB 封裝中,走線密度和信號傳輸速率難以提升,因而內(nèi)存帶寬緩慢增長。而先進封裝的走線密度短,信號傳輸速率有很大的提升空間,同時能大大提高互連密度,因而先進封裝技術(shù)成為解決內(nèi)存墻問題的主要方法之一。

另一方面,高性能處理器的體系架構(gòu)越來越復(fù)雜,晶體管的數(shù)量也在增加,但先進的半導(dǎo)體工藝仍然很昂貴,并且生產(chǎn)率也不令人滿意。

在半導(dǎo)體制造中,芯片面積越小,往往成品率越高。為了降低使用先進半導(dǎo)體技術(shù)的成本并提高良率,一種有效的方法是將大芯片切分成多個小芯片,然后使用先進的封裝技術(shù)將它們連接在一起。

在這一背景下,以臺積電、英特爾、三星為代表的三大芯片巨頭正積極探索 3D 封裝技術(shù)及其他先進封裝技術(shù)。

二、臺積電的3D封裝組合拳

今年 8 月底,臺積電推出 3DFabric 整合技術(shù)平臺,旨在加快系統(tǒng)級方案的創(chuàng)新速度,并縮短上市時間。

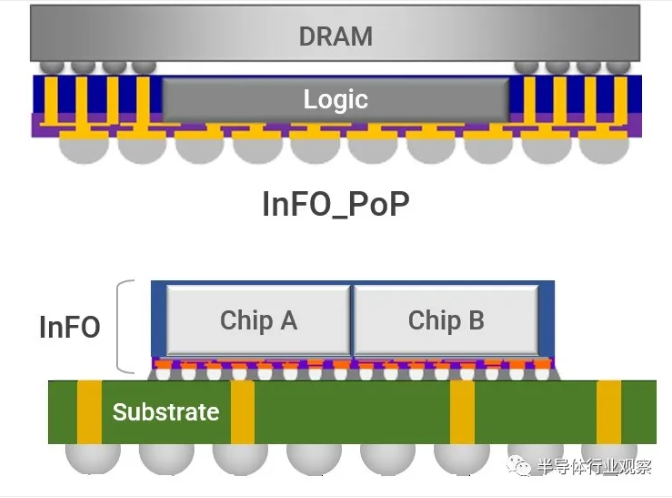

臺積電 3DFabric 可將各種邏輯、存儲器件或?qū)S眯酒c SoC 集成在一起,為高性能計算機、智能手機、IoT 邊緣設(shè)備等應(yīng)用提供更小尺寸的芯片,并且可通過將高密度互連芯片集成到封裝模塊中,從而提高帶寬、延遲和電源效率。

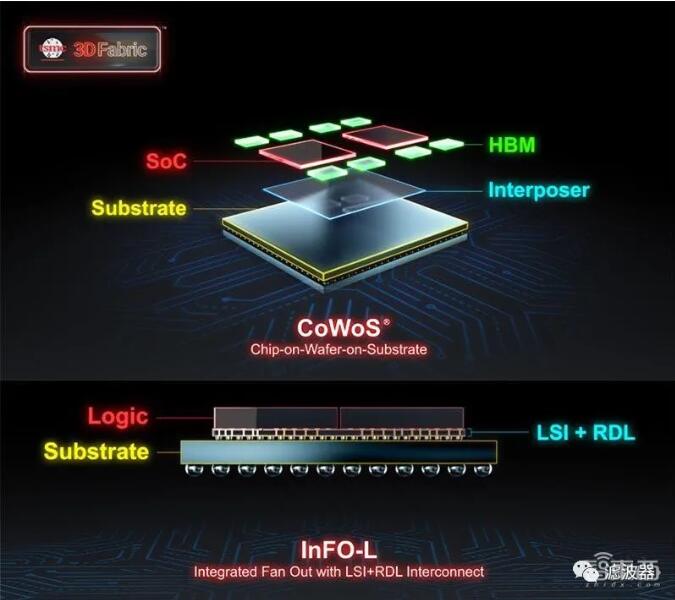

3DFabric 由臺積電前端和后端封裝技術(shù)組成。

前端 3D IC 技術(shù)為臺積電 SoIC 技術(shù),于 2018 年首次對外公布,支持 CoW(Chip on Wafer)和 WoW(Wafer on Wafer)兩種鍵合方式。

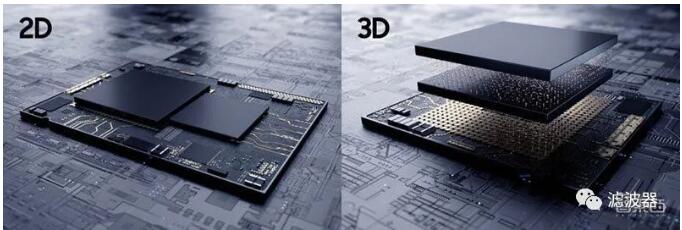

▲ a 為芯片分割前的 SoC;b、c、d 為臺積電 SoIC 服務(wù)平臺支持的多種分區(qū)小芯片和重新集成方案

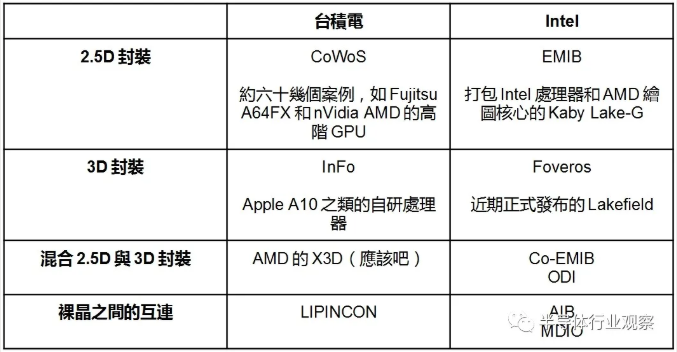

通過采用硅穿孔(TSV)技術(shù),臺積電 SoIC 技術(shù)可達到無凸起的鍵合結(jié)構(gòu), 從而可將不同尺寸、制程、材料的小芯片重新集成到一個類似 SoC 的集成芯片中,使最終的集成芯片面積更小,并且系統(tǒng)性能優(yōu)于原來的 SoC。

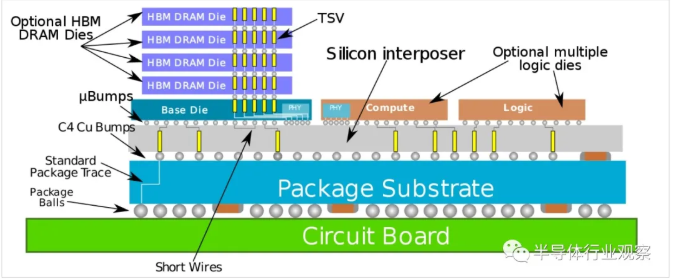

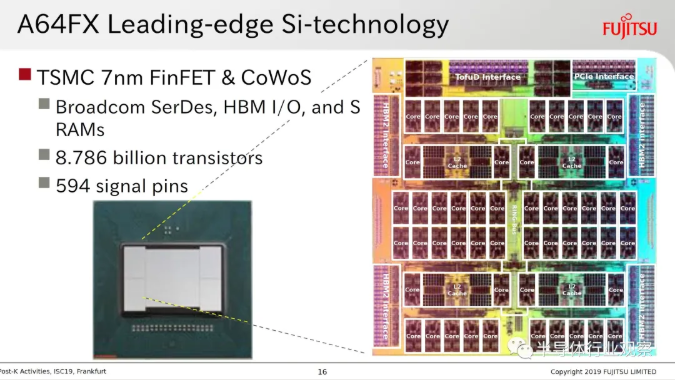

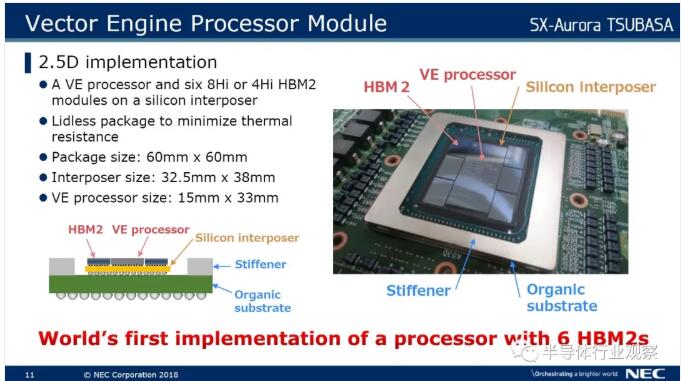

臺積電后端技術(shù)包括 CoWoS(Chip on Wafer on Substrate)和 InFO(Integrated Fan-out)系列封裝技術(shù),已經(jīng)廣泛落地。例如今年全球 TOP 500 超算榜排名[敏感詞]的日本超算 " 富岳 " 所搭載的 Fujitsu A64FX 處理器采用了臺積電 CoWoS 封裝技術(shù),蘋果手機芯片采用了臺積電 InFO 封裝技術(shù)。

此外,臺積電擁有多個專門的后端晶圓廠,負責(zé)組裝和測試包括 3D 堆疊芯片在內(nèi)的硅芯片,將其加工成封裝后的設(shè)備。

這帶來的一大好處是,客戶可以在模擬 IO、射頻等不經(jīng)常更改、擴展性不大的模塊上采用更成熟、更低成本的半導(dǎo)體技術(shù),在核心邏輯設(shè)計上采用[敏感詞]的半導(dǎo)體技術(shù),既節(jié)約了成本,又縮短了新產(chǎn)品的上市時間。

臺積電 3DFabric 將先進的邏輯、高速存儲器件集成到封裝模塊中。在給定的帶寬下,高帶寬內(nèi)存(HBM)較寬的接口使其能以較低的時鐘速度運行,從而減少功耗。

如果以數(shù)據(jù)中心規(guī)模來看,這些邏輯和 HBM 器件節(jié)省的成本十分可觀。

三、英特爾用"分解設(shè)計"策略打出差異化優(yōu)勢

和臺積電相似,英特爾也早已在封裝領(lǐng)域布局了多種維度的先進封裝技術(shù)。

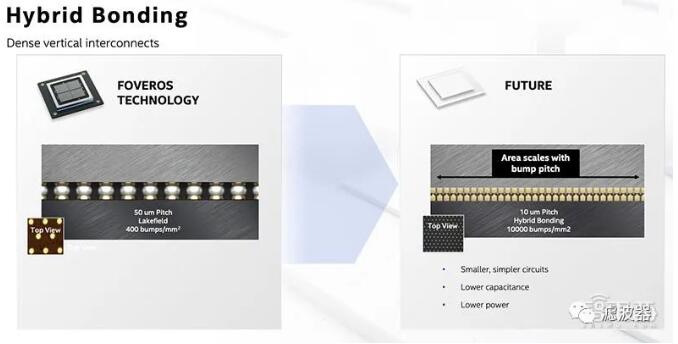

在 8 月 13 日的 2020 年英特爾架構(gòu)日上,英特爾發(fā)布一個全新的混合結(jié)合(Integrated Fan-out)技術(shù),使用這一技術(shù)的測試芯片已在 2020 年第二季度流片。

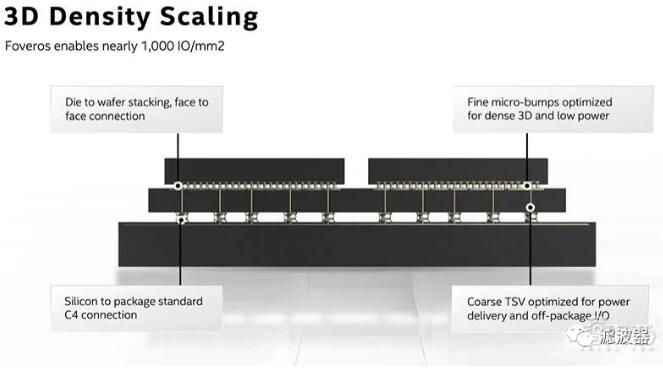

相比當(dāng)前大多數(shù)封裝技術(shù)所使用的熱壓結(jié)合(Thermocompression bonding)技術(shù),混合結(jié)合技術(shù)可將凸點間距降到 10 微米以下,提供更高互連密度、更高帶寬和更低功率。

▲英特爾混合結(jié)合技術(shù)

此前英特爾已推出標(biāo)準(zhǔn)封裝、2.5D 嵌入式多互連橋(EMIB)技術(shù)、3D 封裝 Foveros 技術(shù)、將 EMIB 與 Foveros 相結(jié)合的 Co-EMIB 技術(shù)、全方位互連(ODI)技術(shù)和多模 I/O(MDIO)技術(shù)等,這些封裝互連技術(shù)相互疊加后,能帶來更大的可擴展性和靈活性。

據(jù)英特爾研究院院長宋繼強介紹:" 封裝技術(shù)的發(fā)展就像我們蓋房子,一開始蓋的是茅廬單間,然后蓋成四合院,最后到高樓大廈。以 Foveros 3D 來說,它所實現(xiàn)的就是在建高樓的時候,能夠讓線路以低功率同時高速率地進行傳輸。"

他認為,英特爾在封裝技術(shù)的優(yōu)勢在于,可以更早地知道未來這個房子會怎么搭,也就是說可以更好地對未來芯片進行設(shè)計。

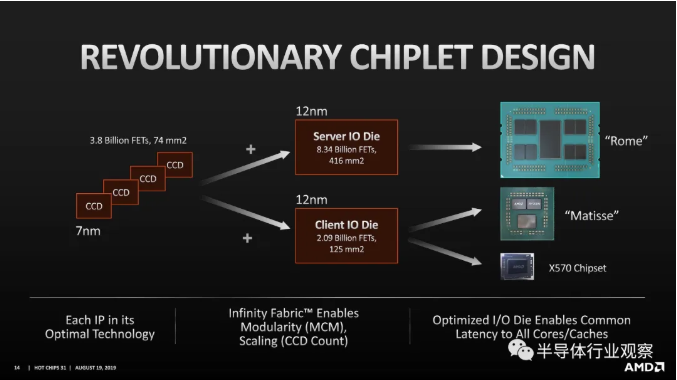

面向未來的異構(gòu)計算趨勢,英特爾推出 " 分解設(shè)計(Digression design)" 策略,結(jié)合新的設(shè)計方法和先進的封裝技術(shù),將關(guān)鍵的架構(gòu)組件拆分為仍在統(tǒng)一封裝中單獨晶片。

也就是說,將原先整個 SoC 芯片 " 化整為零 ",先做成如 CPU、GPU、I/O 等幾個大部分,再將 SoC 的細粒度進一步提升,將以前按照功能性來組合的思路,轉(zhuǎn)變?yōu)榘淳?IP 來進行組合。

這種思路的好處是,不僅能提升芯片設(shè)計效率、減少產(chǎn)品化的時間,而且能有效減少此前復(fù)雜設(shè)計所帶來的 Bug 數(shù)量。

" 原來一定要放到一個晶片上做的方案,現(xiàn)在可以轉(zhuǎn)換成多晶片來做。另外,不僅可以利用英特爾的多節(jié)點制程工藝,也可以利用合作伙伴的工藝。" 宋繼強解釋。

這些分解開的小部件整合起來之后,速度快、帶寬足,同時還能實現(xiàn)低功耗,有很大的靈活性,將成為英特爾的一大差異性優(yōu)勢。

四、三星首秀3D封裝技術(shù),可用于7nm工藝

除了臺積電和英特爾外,三星也在加速其 3D 封裝技術(shù)的部署。

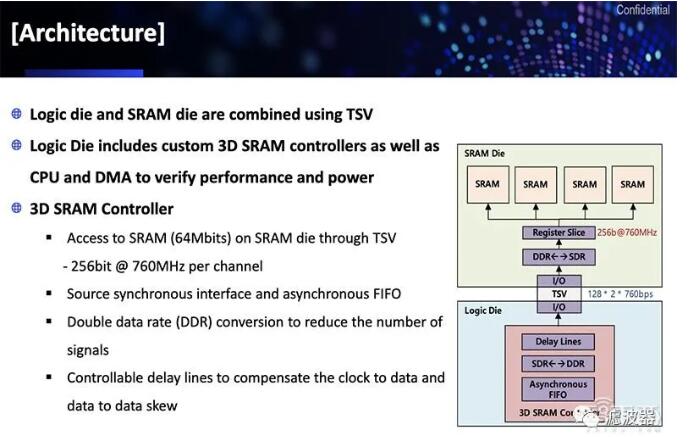

8 月 13 日,三星也公布了其 3D 封裝技術(shù)為 "eXtended-Cube",簡稱 "X-Cube",通過 TSV 進行互連,已能用于 7nm 乃至 5nm 工藝。

據(jù)三星介紹,目前其 X-Cube 測試芯片可以做到將 SRAM 層堆疊在邏輯層上,可將 SRAM 與邏輯部分分離,從而能騰出更多空間來堆棧更多內(nèi)存。

▲三星 X-Cube 測試芯片架構(gòu)

此外,TSV 技術(shù)能大幅縮短裸片間的信號距離,提高數(shù)據(jù)傳輸速度和降低功耗。

三星稱,該 3D 封裝技術(shù)在速度和功效方面實現(xiàn)了重大飛躍,將幫助滿足5G、AI、AR、VR、HPC、移動和可穿戴設(shè)備等前沿應(yīng)用領(lǐng)域的嚴格性能要求。

結(jié)語:三大芯片巨頭強攻先進封裝

可以看到,在 2020 年,圍繞 3D 封裝技術(shù)的戰(zhàn)火繼續(xù)升級,臺積電、英特爾、三星這三大先進芯片制造商紛紛加碼,探索更廣闊的芯片創(chuàng)新空間。

盡管這些技術(shù)方法的核心細節(jié)有所不同,但殊途同歸,都是為了持續(xù)提升芯片密度、實現(xiàn)更為復(fù)雜和靈活的系統(tǒng)級芯片,以滿足客戶日益豐富的應(yīng)用需求。

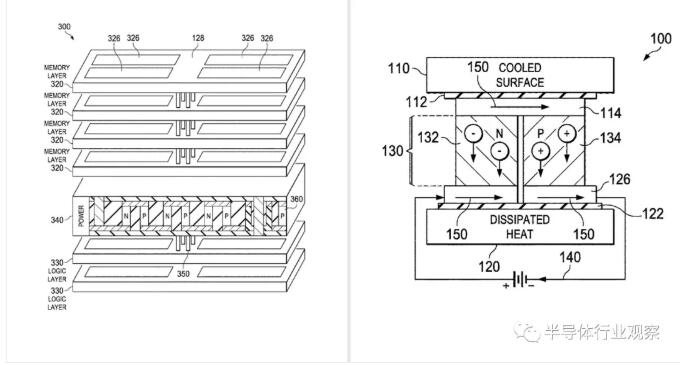

而隨著制程工藝逼近極限,以及應(yīng)用需求的持續(xù)多元化,未來芯片制造商除了要解決散熱等技術(shù)挑戰(zhàn)外,還有望推進來自不同廠商的先進封裝技術(shù)的融合。

二、芯片巨頭決戰(zhàn)先進封裝

轉(zhuǎn)自:半導(dǎo)體行業(yè)觀察

發(fā)展方興未艾的先進封裝技術(shù)

超級電腦用的系統(tǒng)單芯片并非IBM 和Fujitsu 的專利

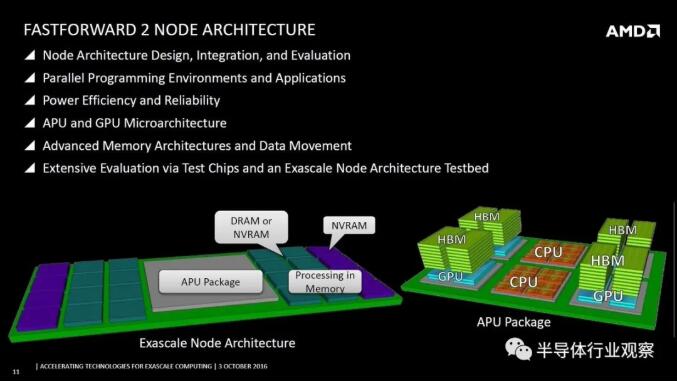

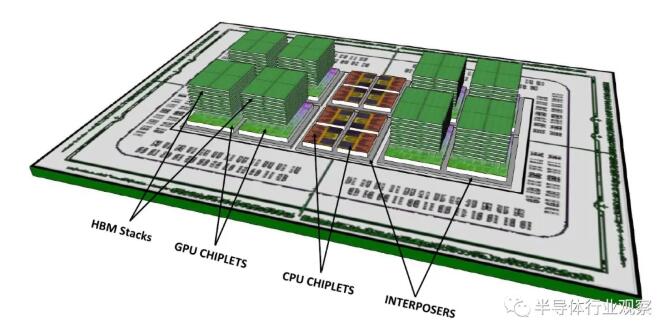

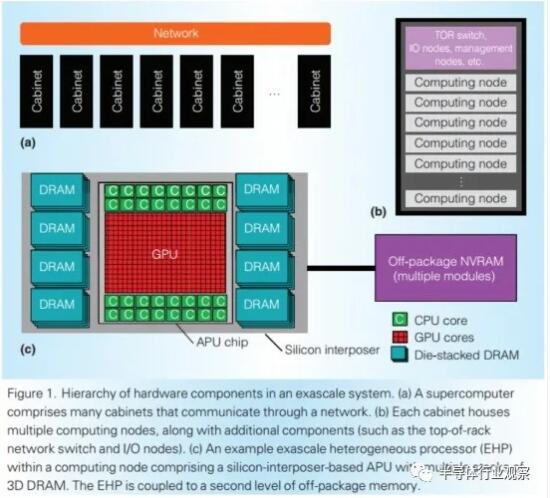

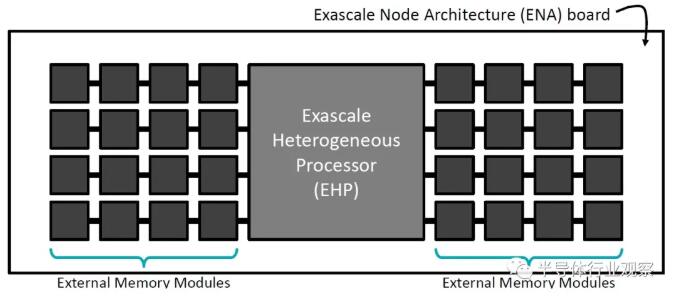

32 個CPU 核心(當(dāng)時是8 顆4 核心CCD)。

8 顆32 個GPU CU,總計256 CU 與16,384 個串流處理器(那時預(yù)定是GCN 第五代的Vega,看來將會推進到CDNA)。

8 塊4GB HBM2 記憶體堆疊。

時脈1GHz 時,雙倍浮點精確度理論效能為16TeraFlops,如十萬顆組成超級電腦,就是1.6ExaFlops,預(yù)估耗電量為20MW。

AMD 在2015 年7 月IEEE Micro 專文,表示32 個CPU 核心、320 個時脈1GHz 的GPU CU(20,480 個串流處理器)、3TB/s 記憶體頻寬、160W 功耗,是能耗比[敏感詞]的組態(tài),總之實際的產(chǎn)品一定會變。

EHP 和X3D 的技術(shù)資產(chǎn)會「推己及人」到Zen 3 世代EPYC 處理器「Milan」的可怕傳言(像10 顆CCD 湊80 核心或塞HBM2 當(dāng)L4 之類的),一直沒有停過。

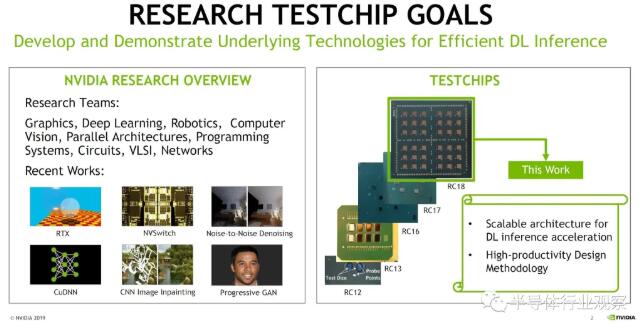

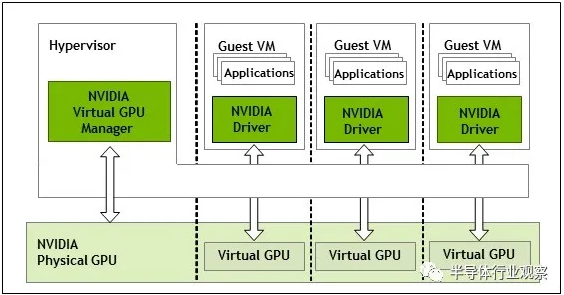

同場加映:nVidia 也沒吃飽閑著

弦外之音:GPU 驅(qū)動程式開源的沖擊

技術(shù)的發(fā)展跟著應(yīng)用的需求走,這恐怕也將會注定AMD 靠著「超級電腦APU」反攻高效能運算市場的企圖能否悲愿成就的鎖鑰。

免責(zé)聲明:本文轉(zhuǎn)載自“濾波器”,本文僅代表作者個人觀點,不代表薩科微及行業(yè)觀點,只為轉(zhuǎn)載與分享,支持保護知識產(chǎn)權(quán),轉(zhuǎn)載請注明原出處及作者,如有侵權(quán)請聯(lián)系我們刪除。

公司電話:+86-0755-83044319

傳真/FAX:+86-0755-83975897

郵箱:1615456225@qq.com

QQ:3518641314 李經(jīng)理

QQ:332496225 丘經(jīng)理

地址:深圳市龍華新區(qū)民治大道1079號展滔科技大廈C座809室

友情鏈接:站點地圖 薩科微官方微博 立創(chuàng)商城-薩科微專賣 金航標(biāo)官網(wǎng) 金航標(biāo)英文站

Copyright ?2015-2024 深圳薩科微半導(dǎo)體有限公司 版權(quán)所有 粵ICP備20017602號